# **Product Preview**

# 0.6 A 2-MHz 100% Duty Cycle Step-Down Synchronous Regulator for Automotive

The NCV890430 is a fixed-frequency Synchronous Buck regulator intended for Automotive, battery-connected applications that operate with up to a 45 V input supply. It is suitable for automotive systems with high efficiency, low noise and Low Shutdown Current requirements that also need to operate at low input voltage close to the output voltage. A reset pin (with adjustable delay) simplifies interfacing with a microcontroller. This part also features an enable input that can either be connected to a low voltage (such as a micro-controller output) or high voltage (such as the battery input), and a synchronization input.

The NCV890430 also provides several protection features expected in automotive power supply systems such as current limit, short circuit protection, and thermal shutdown. In addition, the high switching frequency produces low output voltage ripple even when using small inductor values and all-ceramic input output filter capacitors — forming a space-efficient switching regulator solution

#### Features

- Internal 500 m $\Omega$  P-channel and 250 m $\Omega$  N-channel Power Switches

- Capable of 100% Duty Cycle Operation

- V<sub>IN</sub> Operating Range 3.5 V to 37 V

- Withstands Load Dump to 45 V

- 2 MHz Free-running Switching Frequency

- Low Shutdown Current < 10 μA

- High Voltage Enable Pin

- Synchronization Input Pin

- DC Output Current of at Least 0.6 A

- Fixed Output Voltage (5 V, 3.3 V, 2.5 V, 1.8 V Versions)

- ±2% Output Voltage Accuracy

- NCV Prefix for Automotive Requiring Site and Control Changes

- DFN Package with Wettable Flanks (Pin Edge Plating per JEDEC MO220)

#### **Typical Applications**

- Automotive Infotainment and Instrumentation

- Automotive Body Applications

- Linear Regulator Replacement

- Rear View Camera

#### ON Semiconductor®

www.onsemi.com

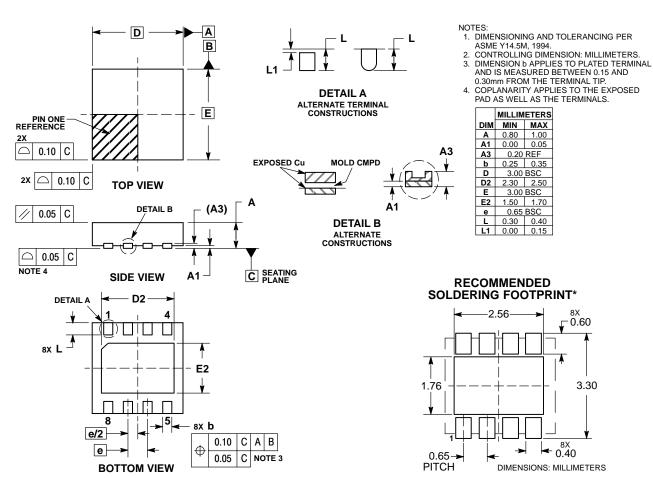

DFN8, 3x3, 0.65P CASE 506CS

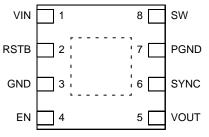

#### PIN CONNECTIONS

(DFN8 Top View)

#### **MARKING DIAGRAM**

XXXXX = Specific Device Code (TBD)

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering, marking and shipping information in the package dimensions section on page 8 of this data sheet.

This document contains information on some products that are still under development. ON Semiconductor reserves the right to change or discontinue these products without notice.

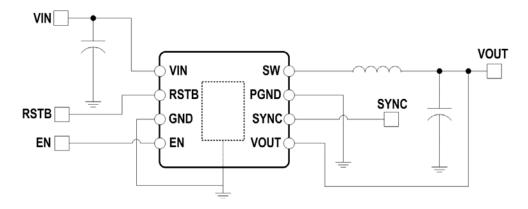

Figure 1. Typical Application Schematic

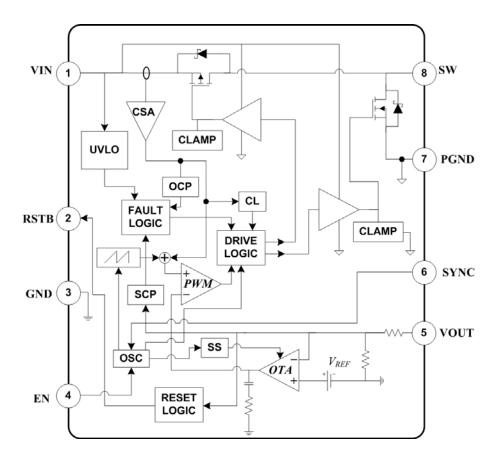

Figure 2. Simplified Block Diagram

**Table 1. PIN FUNCTION DESCRIPTIONS**

| Pin No.     | Pin Name | Description                                                                                                                                                                                                    |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1           | VIN      | Input voltage from battery. Place an input filter capacitor in close proximity to this pin.                                                                                                                    |  |  |

| 2           | RSTB     | Reset reporting flag. Open drain output, pulling down to ground when the output voltage is out of regulation. The value of the external pull-up resistor determines the delay time that the Reset is held low. |  |  |

| 3           | GND      | Analog ground reference – should be connected directly to the output capacitor ground and the exposed pad.                                                                                                     |  |  |

| 4           | EN       | Enable input. Connecting a "high" voltage (TTL compatible, battery voltage tolerant) to this pin turns on the regulator. A low voltage forces the part into a very low lq shutdown mode.                       |  |  |

| 5           | VOUT     | Output voltage sensing for regulation.                                                                                                                                                                         |  |  |

| 6           | SYNC     | Synchronization input. Connecting an external clock to this pin synchronizes switching to the rising edge of the SYNC signal.                                                                                  |  |  |

| 7           | PGND     | Power ground, connect directly to the input capacitor ground and to the exposed pad.                                                                                                                           |  |  |

| 8           | SW       | Switching node of the Regulator. Connect the output inductor to this pin.                                                                                                                                      |  |  |

| Exposed Pad | EPAD     | Must be connected to GND (pin 3, electrical ground) and to a low thermal resistance path to the ambient temperature environment                                                                                |  |  |

## **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                | Symbol           | Value        | Unit |

|-------------------------------------------------------|------------------|--------------|------|

| Min/Max Voltage VIN                                   |                  | -0.3 to 45   | V    |

| Max Voltage VIN to SW                                 |                  | 45           | V    |

| Min/Max Voltage SW                                    |                  | –0.7 to 40 V | V    |

| Min Voltage SW – 20 ns                                |                  | -3.0         | V    |

| Min/Max Voltage EN                                    |                  | –0.3 to 40 V | V    |

| Min/Max Voltage on SYNC, RSTB                         |                  | -0.3 to 6    | V    |

| Min/Max Voltage VOUT                                  |                  | -0.3 to 18   | V    |

| Thermal Resistance, DFN8 Junction-to-Ambient (Note 1) | $R_{	heta JA}$   | 40           | °C/W |

| Storage Temperature Range                             |                  | -55 to +150  | °C   |

| Operating Junction Temperature Range                  | T <sub>J</sub>   | -40 to +150  | °C   |

| ESD withstand Voltage (Human Body Model)              | V <sub>ESD</sub> | 2.0          | kV   |

| Moisture Sensitivity                                  | MSL              | Level 1      |      |

| Peak Reflow Soldering Temperature (Note 1)            |                  | 260          | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Mounted on 1 sq. in. of a 4-layer PCB with 1 oz. copper thickness.

## **Table 3. ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 4.5 \text{ V to } 28 \text{ V}, \text{ EN} = 5 \text{ V}. \text{ Min/Max values are valid for the temperature range } -40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Parameter                                                                         | Test Conditions                                                                                   | Symbol                                     | Min                           | Тур                      | Max                           | Unit |  |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------|--------------------------|-------------------------------|------|--|--|--|

| QUIESCENT CURRENT                                                                 |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| Quiescent Current, Enabled                                                        | V <sub>IN</sub> = 13.2 V                                                                          | I <sub>qEN</sub>                           |                               |                          | 3                             | mA   |  |  |  |

| uiescent Current, Shutdown V <sub>IN</sub> = 13.2 V, V <sub>EN</sub> = 0 V, 25 °C |                                                                                                   | I <sub>qSD</sub>                           |                               |                          | 5                             | μΑ   |  |  |  |

| UNDERVOLTAGE LOCKOUT – VIN                                                        |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| UVLO Start Threshold                                                              | V <sub>IN</sub> Rising                                                                            | V <sub>UVLSTT</sub>                        | 4.1                           |                          | 4.5                           | V    |  |  |  |

| UVLO Stop Threshold                                                               | V <sub>IN</sub> Falling                                                                           | V <sub>UVLSTP</sub>                        | 3.2                           |                          | 3.5                           | V    |  |  |  |

| SOFT-START                                                                        |                                                                                                   |                                            |                               | •                        |                               | •    |  |  |  |

| Soft-Start Completion Time                                                        |                                                                                                   | t <sub>SS</sub>                            | 0.8                           | 1.4                      | 2.0                           | ms   |  |  |  |

| OUTPUT VOLTAGE                                                                    |                                                                                                   |                                            |                               | •                        |                               | •    |  |  |  |

| Output Voltage during Regulation                                                  | 100 μA < I <sub>OUT</sub> < 0.6 A<br>5.0 V Option<br>3.3 V Option<br>2.5 V Option<br>1.8 V Option | V <sub>OUTreg</sub>                        | 4.9<br>3.234<br>2.45<br>1.764 | 5.0<br>3.3<br>2.5<br>1.8 | 5.1<br>3.366<br>2.55<br>1.836 | V    |  |  |  |

| OSCILLATOR                                                                        |                                                                                                   | •                                          |                               | !                        |                               | !    |  |  |  |

| Frequency                                                                         | 4.5 V < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V                                   | f <sub>SW</sub>                            | 1.8<br>0.9                    | 2.0<br>1.0               | 2.2<br>1.1                    | MHz  |  |  |  |

| VBAT OVERVOLTAGE SHUTDOWN MONIT                                                   | OR                                                                                                |                                            |                               | •                        |                               | •    |  |  |  |

| Overvoltage Stop Threshold                                                        |                                                                                                   | V <sub>OV1SP</sub>                         | 37                            |                          | 40                            | V    |  |  |  |

| Overvoltage Start Threshold                                                       |                                                                                                   | V <sub>OV1ST</sub>                         | 34                            |                          |                               | V    |  |  |  |

| Overvoltage Hysteresis                                                            |                                                                                                   | V <sub>OV1HY</sub>                         | 0.6                           |                          | 2.7                           | V    |  |  |  |

| VIN FREQUENCY FOLDBACK MONITOR                                                    |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| Frequency Foldback Threshold                                                      | V <sub>IN</sub> Rising<br>V <sub>IN</sub> Falling                                                 | V <sub>FLDUP</sub><br>V <sub>FLDDN</sub>   | 18.4<br>18                    |                          | 20<br>19.8                    | V    |  |  |  |

| Frequency Foldback Hysteresis                                                     |                                                                                                   | V <sub>FLDHY</sub>                         | 0.2                           | 0.3                      | 0.4                           | V    |  |  |  |

| PEAK CURRENT LIMIT                                                                |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| Current Limit Threshold                                                           |                                                                                                   | I <sub>LIM</sub>                           | 1.5                           | 1.7                      | 1.9                           | Α    |  |  |  |

| Low-Side Current Limit Threshold                                                  | V <sub>SW</sub> = 13.2 V                                                                          | I <sub>LIMLS</sub>                         |                               | 1.5                      |                               | Α    |  |  |  |

| POWER SWITCHES                                                                    |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| High-Side Switch ON Resistance                                                    |                                                                                                   | R <sub>DSON-HS</sub>                       |                               |                          | 1000                          | mΩ   |  |  |  |

| Low-Side Switch ON Resistance                                                     |                                                                                                   | R <sub>DSON-LS</sub>                       |                               |                          | 500                           | mΩ   |  |  |  |

| Leakage Current V <sub>IN</sub> to SW                                             | $V_{SW} = 0, -40^{\circ}C \le T_{J} \le 85^{\circ}C$                                              | I <sub>LKSWH</sub>                         |                               |                          | 10                            | μΑ   |  |  |  |

| Leakage Current SW to GND                                                         | $V_{SW} = 13.2 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                   | I <sub>LKSWL</sub>                         |                               |                          | 10                            | μΑ   |  |  |  |

| Minimum ON Time                                                                   | Measured at SW Pin                                                                                | t <sub>ONMIN</sub>                         | 45                            |                          | 70                            | ns   |  |  |  |

| Minimum OFF Time when Not 100% Duty Cycle                                         | Measured at SW Pin at f <sub>SW</sub> = 2 MHz                                                     | t <sub>OFFMIN</sub>                        |                               | 30                       | 50                            | ns   |  |  |  |

| Non-Overlap Time                                                                  |                                                                                                   | t <sub>NOVLP</sub>                         |                               | 10                       |                               | ns   |  |  |  |

| SLOPE COMPENSATION                                                                |                                                                                                   |                                            |                               |                          |                               |      |  |  |  |

| Ramp Slope (Note 2)<br>(With Respect to Switch Current)                           | 4.5 V < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V                                   | S <sub>ramp</sub><br>S <sub>ramp(HV)</sub> | 1.05<br>0.5                   | 1.5<br>0.75              | 1.95<br>1                     | A/μs |  |  |  |

## Table 3. ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = 4.5 \text{ V to } 28 \text{ V}, \text{ EN} = 5 \text{ V}. \text{ Min/Max values are valid for the temperature range } -40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C} \text{ unless noted otherwise,}$ and are guaranteed by test, design or statistical correlation.)

| Parameter                                                                                                                 | Test Conditions                                                                                                   | Symbol                                     | Min        | Тур            | Max        | Unit           |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------|----------------|------------|----------------|

| SHORT CIRCUIT FREQUENCY FOLDBACK                                                                                          |                                                                                                                   |                                            |            |                |            |                |

| Switching Frequency in Short-Circuit Condition Lowest Foldback Frequency Lowest Foldback Frequency – High V <sub>IN</sub> | V <sub>OUT</sub> = 0 V, 4.5 V < V <sub>IN</sub> < 18 V<br>V <sub>OUT</sub> = 0 V, 20 V <v<sub>IN &lt; 28V</v<sub> | f <sub>SWAF</sub>                          | 450<br>225 | 550<br>275     | 650<br>325 | kHz            |

| HICCUP MODE                                                                                                               |                                                                                                                   | <b>3</b>                                   |            |                | Į          |                |

| Hiccup Mode                                                                                                               | V <sub>SW</sub> = 0 V                                                                                             | f <sub>SWHIC</sub>                         | 24         | 32             | 40         | kHz            |

| Hiccup Mode 2 – SW Short to Battery                                                                                       | V <sub>SW</sub> = 13.2 V                                                                                          | fswhicls                                   | 24         | 32             | 40         | kHz            |

| SYNCHRONIZATION                                                                                                           |                                                                                                                   |                                            |            |                |            | I              |

| SYNC Input Resistance to Ground                                                                                           | V <sub>SYNC</sub> = 5.0 V                                                                                         | R <sub>H(SYNC)</sub>                       | 50         |                | 200        | kΩ             |

| SYNC Input High Threshold Voltage                                                                                         |                                                                                                                   | V <sub>HSYNC</sub>                         | 2.0        |                |            | V              |

| SYNC Input Low Threshold Voltage                                                                                          |                                                                                                                   | V <sub>LSYNC</sub>                         |            |                | 0.8        | V              |

| SYNC High Pulse Width                                                                                                     | V <sub>SYNC</sub> > max V <sub>HSYNC</sub>                                                                        | t <sub>HSYNC</sub>                         | 40         |                |            | ns             |

| SYNC Low Pulse Width                                                                                                      | V <sub>SYNC</sub> < min V <sub>LSYNC</sub>                                                                        | t <sub>LSYNC</sub>                         | 40         |                |            | ns             |

| External SYNC Frequency                                                                                                   |                                                                                                                   | f <sub>SYNC</sub>                          | 1.8        |                | 2.5        | MHz            |

| Master Reassertion Time                                                                                                   | Time from Last Rising SYNC Edge to First Un-synchronized Turn-on.                                                 | t <sub>I(SYNC)</sub>                       |            | 650            |            | ns             |

| RESET                                                                                                                     |                                                                                                                   |                                            |            | •              |            | l              |

| Reset Threshold                                                                                                           | V <sub>OUT</sub> Decreasing<br>V <sub>OUT</sub> Increasing                                                        | K <sub>RES_LO</sub><br>K <sub>RES_HI</sub> | 90<br>90.5 | 92.5           | 95<br>97   | %              |

| Reset Hysteresis (Ratio of VOUT)                                                                                          |                                                                                                                   | K <sub>RES_HYS</sub>                       | 0.5        |                |            | %              |

| Leakage Current into RSTB Pin                                                                                             |                                                                                                                   |                                            |            |                | 1          | μΑ             |

| Noise-Filtering Delay                                                                                                     | From V <sub>OUT</sub> < V <sub>RESET</sub> to RSTB Pin<br>Going Low                                               | t <sub>RES_FILT</sub>                      | 10         |                | 25         | μs             |

| Reset Delay Time                                                                                                          | I <sub>RSTB</sub> = 1 mA<br>I <sub>RSTB</sub> = 500 μA<br>I <sub>RSTB</sub> = 100 μA                              | t <sub>RESET</sub>                         | TBD<br>TBD | 1.0<br>5<br>25 | TBD<br>TBD | μs<br>ms<br>ms |

| Reset Delay Modes                                                                                                         | Power Good Mode (No Delay)<br>Delay Mode                                                                          |                                            | 900        |                | 600        | μΑ             |

| Reset Output Low Level                                                                                                    | I <sub>RSTB</sub> = 1 mA                                                                                          | V <sub>RESL</sub>                          |            |                | 0.4        | V              |

| ENABLE                                                                                                                    |                                                                                                                   | •                                          |            |                |            |                |

| Logic Low Threshold Voltage                                                                                               |                                                                                                                   | V <sub>ENIow</sub>                         |            |                | 0.8        | V              |

| Logic High Threshold Voltage                                                                                              |                                                                                                                   | V <sub>ENhigh</sub>                        | 2          |                |            | V              |

| EN Pin Input Current                                                                                                      |                                                                                                                   | I <sub>ENbias</sub>                        | 8.0        |                | 30         | μΑ             |

| THERMAL SHUTDOWN                                                                                                          |                                                                                                                   |                                            |            |                |            |                |

| Thermal Shutdown Activation Temperature (Note 2)                                                                          |                                                                                                                   | T <sub>SD</sub>                            | 150        |                | 190        | °C             |

| Hysteresis (Note 2)                                                                                                       |                                                                                                                   | T <sub>HYS</sub>                           | 5          |                | 20         | °C             |

|                                                                                                                           | n the Fleetrical Characteristics for the                                                                          |                                            |            |                |            | Draduat        |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Not tested in production. Limits are guaranteed by design.

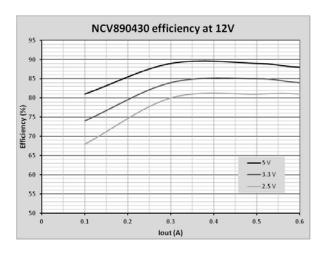

## **TYPICAL CURVES**

Figure 3. Typical Efficiency vs. Output Current at  $V_{\text{IN}}$  = 12 V

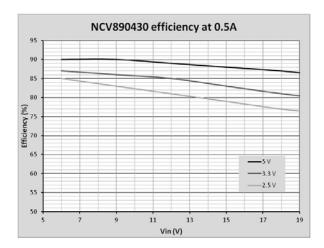

Figure 4. Typical Efficiency vs. Input Voltage at  $I_{OUT} = 0.5 A$

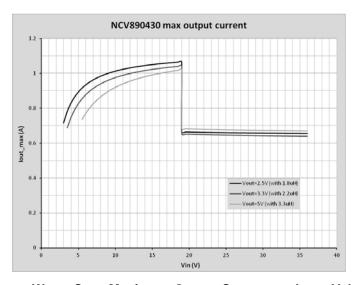

Figure 5. Worst Case Maximum Output Current vs. Input Voltage

#### **APPLICATION INFORMATION**

#### **General Description**

The NCV890430 is a high-frequency synchronous switch-mode regulator with current-mode control, fixed output voltage and fixed internal closed-loop compensation, accepting a wide input voltage range typical to automotive applications.

The use of a P-channel high-side MOSFET simplifies the driving scheme (no bootstrap circuitry needed), and enables a duty cycle of 100% for low dropout operation at low input voltage.

#### Input Voltage

An Undervoltage Lockout (UVLO) circuit monitors the input, and can inhibit switching and reset the soft-start circuit if there is insufficient voltage for proper regulation. Depending on the output conditions (voltage option and loading), the NCV890430 may lose regulation and run in drop-out mode before reaching the UVLO threshold: refer to the Minimum  $V_{\rm IN}$  calculation tool for details. When the

input voltage drops low enough that the part cannot regulate because it reaches its maximum duty cycle, the high-side MOSFET can turn on permanently (100% duty cycle operation), to help lower the minimum voltage at which the regulator loses regulation.

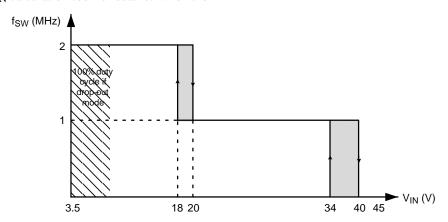

An overvoltage monitoring circuit automatically terminates switching if the input voltage exceeds 37~V (see Figure 6), but the NCV890430 can withstand input voltages up to 45~V.

To avoid skipping switching pulses and enter an uncontrolled mode of operation, the switching frequency is reduced by a factor of 2 when the input voltage exceeds the  $V_{\rm IN}$  Frequency Foldback threshold (see Figure 6 below). Frequency reduction is automatically terminated when the input voltage drops back below the  $V_{\rm IN}$  Frequency Foldback threshold. This also helps to limit the power lost in switching and generating the drive voltage for the Power Switches at high input voltage.

Figure 6. NCV890430 Worst-Case Switching Frequency Profile vs. Input Voltage

#### Soft-Start

Upon being enabled or released from a fault condition, a soft-start circuit ramps the switching regulator error amplifier reference voltage to the final value, forcing the output to follow the same soft-start ramp. During soft-start, the average switching frequency is lower until the output voltage approaches regulation.

#### **Slope Compensation**

A fixed slope compensation signal is generated internally and added to the sensed current to avoid increased output voltage ripple due to bifurcation of inductor ripple current at duty cycles above 50%. The fixed amplitude of the slope compensation signal requires the inductor to be greater than a minimum value, depending on output voltage, in order to avoid sub-harmonic oscillations. The recommended inductor value is between 1.8 and 3.3  $\mu H_{\rm s}$ , although other values are possible.

#### **Current Limiting**

Due to the ripple on the inductor current, the average output current of a buck converter is lower than the peak current set point of the regulator. See "typical curves" for how the variation of inductor peak current with input voltage affects the maximum dc current the NCV890430 can deliver to a load.

#### **Short Circuit Protection**

During severe output overloads or short circuits, the NCV890430 automatically reduces its switching frequency. This creates duty cycles small enough to limit the peak current in the power components, while maintaining the ability to automatically reestablish the output voltage if the overload is removed.

In more severe short-circuit conditions where the inductor current reaches the peak current limit during the minimum on time, the regulator enters a hiccup mode that further reduces the power dissipation and protects the system.

#### **RESET Function**

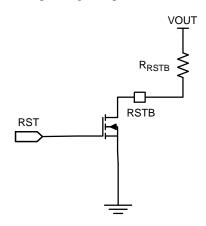

The RSTB pin is pulled low when the output voltage falls below 6.5 % of the nominal regulation level, and floats when the output is properly regulated. A pull-up resistor tied to the output is needed to generate a logic high signal on this open-drain pin. The pin can be left unconnected when not used.

When the output voltage drops out of regulation, the pin goes low after a short noise-filtering delay (K<sub>RES\_FILT</sub>). It stays low for a delay time (adjustable) after the output goes back to regulation, simplifying the connection to a micro-controller.

The RSTB signal can either be used as a reset with delay or a power good (no delay). The delay is determined by the current into the RSTB pin, set by a resistor, as shown in Figure 7.

Use the following equation to determine the ideal reset delay time using currents less than 1 mA:

$$t_{\text{delay}} = \frac{2500}{I_{\text{RSTB}}} \tag{eq. 1}$$

where:  $t_{delay}$  is the ideal reset delay time [ms]  $I_{RSTB}$  is the current into the RSTB pin [ $\mu$ A]

Using  $I_{RSTB} = 1$  mA removes the delay and allows the reset to act as a "power good" pin.

Figure 7. Reset with Adjustable Delay on a Single Pin

The RSTB resistor is commonly tied to VOUT. Depending on the output voltage option, typical delay times can be achieved with the following resistor values:

**Table 4. TYPICAL DELAY TIMES**

| R <sub>RSTB</sub> (kΩ) | t <sub>delay</sub> (ms) – 5 V | t <sub>delay</sub> (ms) – 3.3 V | t <sub>delay</sub> (ms) – 2.5 V | t <sub>delay</sub> (ms) – 1.8 V |

|------------------------|-------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 5                      | -                             | -                               | 5                               | 6.9                             |

| 10                     | 5                             | 7.6                             | 10                              | 14                              |

| 20                     | 10                            | 15                              | 20                              | -                               |

| 30                     | 15                            | 23                              | -                               | -                               |

| 50                     | 25                            | -                               | -                               | -                               |

#### **Enable**

The NCV890430 is designed to accept either a logic-level signal or battery voltage as an Enable signal. However, if voltages above 40 V are expected, EN should be tied to VIN through a 10  $k\Omega$  resistor in order to limit the current flowing into the overvoltage protection of the pin.

A low signal on Enable induces a shutdown mode which shuts off the regulator and minimizes its supply current to less than  $5 \mu A$  by disabling all functions.

Once the switching regulator output is enabled, a soft-start is always initiated.

#### **Thermal Shutdown**

A thermal shutdown circuit inhibits switching and resets the soft-start circuit if internal temperature exceeds a safe level. Switching is automatically restored when temperature returns to a safe level.

#### **Exposed Pad**

The exposed pad (EPAD) on the back of the package must be electrically connected to both the analog and the power electrical ground GND and PGND pins for proper, noise-free operation.

#### **DEVICE ORDERING INFORMATION**

| Device           | Output | Marking | Package   | Shipping <sup>†</sup> |  |

|------------------|--------|---------|-----------|-----------------------|--|

| NCV890430MW50TXG | 5.0 V  | TBD     |           |                       |  |

| NCV890430MW33TXG | 3.3 V  | TBD     | DFN8      | TBD / Tape & Reel     |  |

| NCV890430MW25TXG | 2.5 V  | TBD     | (Pb-Free) |                       |  |

| NCV890430MW18TXG | 1.8 V  | TBD     |           |                       |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### PACKAGE DIMENSIONS

#### DFN8, 3x3, 0.65P CASE 506CS ISSUE O

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent—Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative